【LPC54100】在M0上跑事件驱动构架(二)

时间:2015-12-03 11:17:34

收藏:0

阅读:289

@20150216

一些新玩意

1.总线矩阵

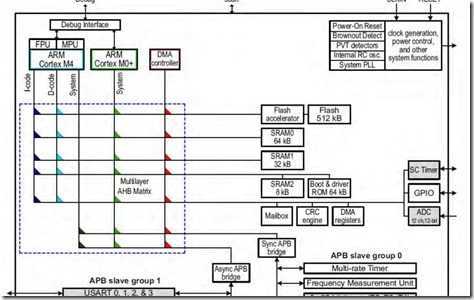

如下图所示,M4及M0核分别通过各自的总线访问外设,

两个核心所使用的外设地址是相同的,当他们同时访问相同外设时,就会产生竞争,其中一个核心被阻塞。所以最好让一个核心在SRAM0或SRAM1中运行。

2.中断管理

之前玩单核MCU,并没有注意到NVIC是与arm核紧密耦合的,在研究LPC54100时才注意到两个核心各有一个NVIC,用于控制该核心对外设中断的响应。

在LPC54100中,NVIC寄存器的地址是一致的,但是每个核心访问这些基础器时,实际操作的寄存器是不一样的,这一点不同于公用外设。在《LPC5410x User manual》中有下面这句话:

3.启动过程

LPC54102中有一块ROM区域,里面是M4核心的固化代码,复位后,m0核心并不运行,m4核心从rom中启动,之后引导M0核心。

由于这个差异,在单独调试M0核遇到了一些问题,这点需要注意。

这部分可参看《AN11609_LPC54xxx_DualCore_v1.0.pdf》

原文:http://www.cnblogs.com/leop/p/5015346.html

评论(0)